据三星官方消息,面向高性能计算(HPC)的 HBM 内存迎来新进展,9.8Gbps 的 HBM3E 产品已开始向客户提供样品,而 HBM4 内存预计 2025 年推出。

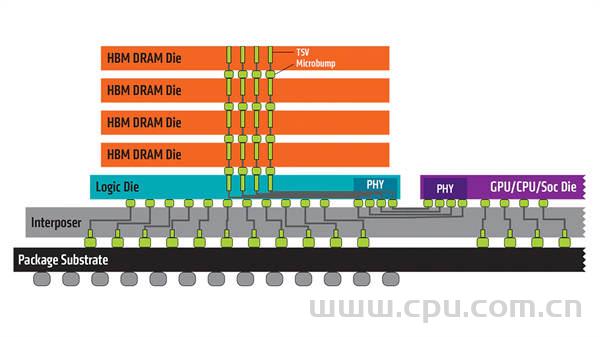

虽然目前还没有关于 HBM4 的正式规范,但台积电在 2023 OIP 论坛阿姆斯特丹厂上给出了部分制定中的标准。台积电称,未来 HBM4 内存的接口位宽将实现翻倍,达到 2048 bit。

值得一提的是,出于多种技术原因,他们还希望在不增加 HBM 内存堆栈占用空间的情况下实现这一目标,这也将会使得下一代 HBM 内存的互连密度翻倍,而无需进一步提高时钟速度。

按照计划,这将使 HBM4 在多种技术层面上实现重大飞跃。

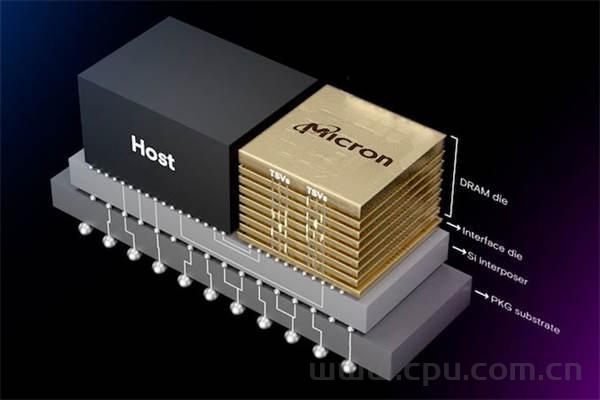

在 DRAM 堆叠方面,一个 2048bit 的内存接口需要大幅增加硅通孔的数量。同时,外部芯片接口将需要将凸块间距缩小到 55 微米以下,同时大幅增加微凸块数目(HBM3 目前大约 3982 个微凸块)。

此外,HBM4 还将采用 16-Hi 堆叠模式,也就是说在一个模块中堆叠 16 个内存芯片,这也将致使其技术复杂性进一步提高 (HBM3 从技术层面上来讲也支持 16-Hi 堆叠,但到目前为止还没有哪家制造商实际这么干过)。

所有这些新指标反过来都需要芯片制造商、内存制造商和芯片封装公司之间采取更加紧密的合作方式,以确保一切顺利地进行。

在台积电于阿姆斯特丹举行的 TSMC OIP 2023 会议上,台积电设计基础设施管理负责人丹・科赫帕恰林(Dan Kochpatcharin)表示:“因为他们没有将速度加倍,而是将 [接口] 引脚 [与 HBM4 一起] 加倍。这就是为什么我们正在努力确保我们与所有三个合作伙伴合作,使他们的 HBM4 [可以通过我们的先进封装] 合格,并确保 RDL 或中介器或两者之间的任何内容都可以支持 HBM4 的布局和速度。所以,我们正在与三星、SK 海力士和美光保持合作。”